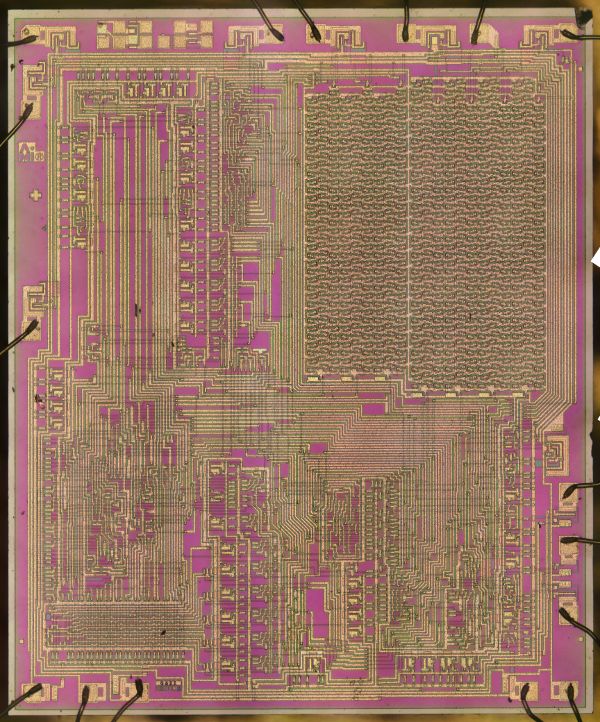

| HP-35 chip images and schematics Message #1 Posted by Peter Monta on 24 Oct 2010, 7:44 p.m. After seeing the nice work from the Visual 6502 people (http://visual6502.org/) and the 4004 project (http://www.4004.com/), I thought it would be interesting to do something similar for the HP-35 chips. While emulators at the instruction-set level work fine, simulating the original implementation at the transistor level has a number of advantages: - makes no assumptions about the microarchitecture---guaranteed to be bit-exact to the hardware - can be used for cross-testing against other emulators and against the hardware - provides complete, unambiguous documentation of the original implementation - the derived masks can be used to make new chips - the circuits can be automatically translated to switch-level HDL and run on FPGAs So far I've got images of two chips (the A&R chip and one of the ROMs) and a schematic of one stage of the ROM address shift register. This is only a tiny part of the required work, but I thought I'd at least get the images out there so that anyone else who's interested can extract transistor netlists for other parts of the chips. Thumbnails of the chip images, an annotated closeup of the shift-register circuit, and the corresponding schematic are shown below. A&R chip (AMI 1820-0848):

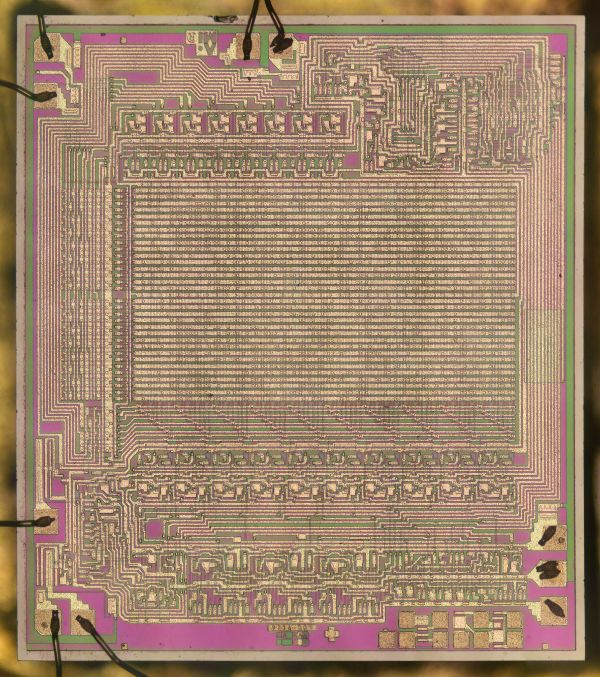

ROM chip (AMI 1818-0006):

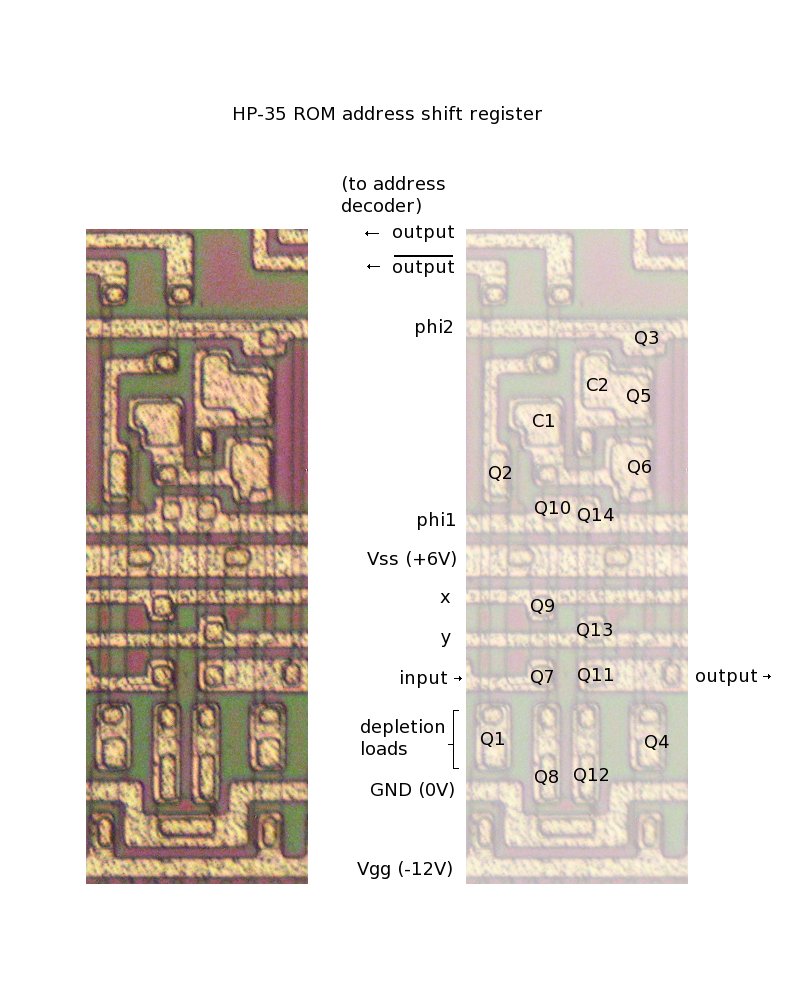

ROM shift register closeup:

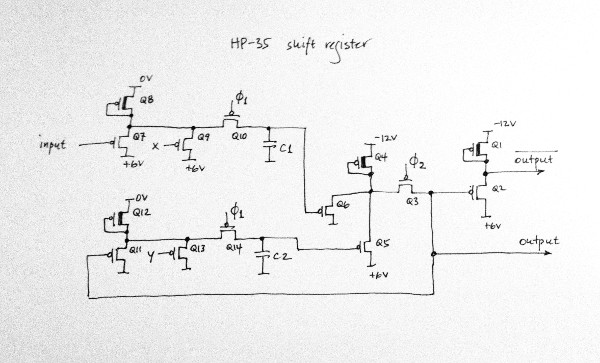

Schematic of the chip fragment above:

The full, high-resolution images can be found here: http://pmonta.com/calculators/hp-35/chips/ My uplink is a DSL line, so it may be slow. For the imaging workflow, very modest equipment was used (which was part of the fun): a $160 beginner's microscope with a generic 10x achromat objective, a hacked-up epi illuminator, an afocally-coupled Canon point-and-shoot camera running the free CHDK firmware, and hugin for image processing. The images have some places where the focus is less than perfect. I hope to fix that in future by taking a focus series at each subimage ("focus stacking") before assembling the panorama. |