| New HP-12C Review Message #1 Posted by Katie Wasserman on 27 Apr 2009, 6:47 p.m. Thanks entirely to Charlie Oxford's efforts I now have a new HP-12C to play with.

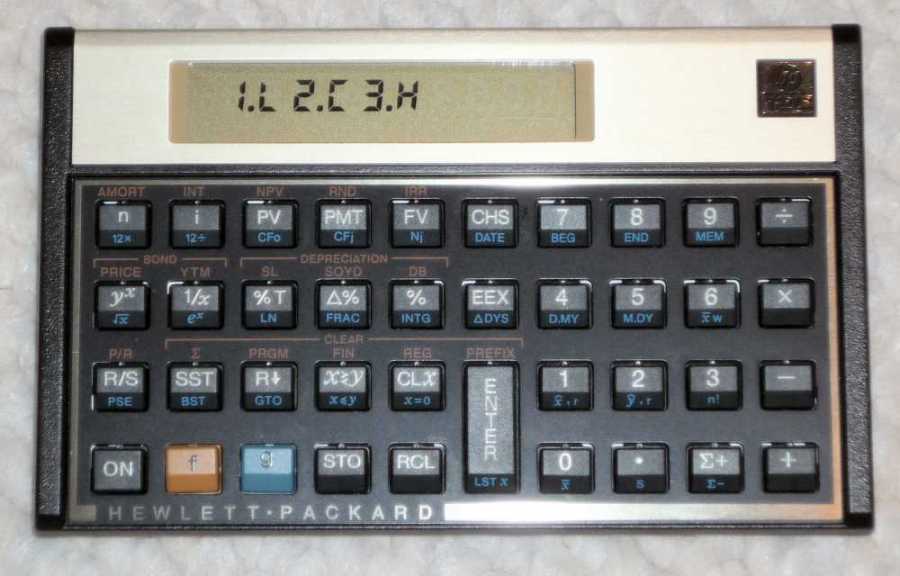

If you like the original 12C you will love this machine. It's functionally identical to the original (we know this because it's emulating the original) but everything runs 60 (sixty) times faster: a long program (my 70 decimal digits of pi) ran in 90 seconds vs 90 minutes on the original 12C; a long amortization, 1.5 seconds vs 90 seconds, 69 factorial gives you an answer almost before you hit the key, it's ludicrously fast! I hope that this blazing speed does not scar the set-in-their-ways wall street crowd from believing the calculation results. Build quality, key clicks and display readability are excellent. Most importantly, no missed keystrokes. The keys themselves use the new, lower density plastic compared to the original, but this is a very minor nit to pick. The only things that are functionally different are the self tests. The manual has not been updated in this section, so it's wrong in most cases: - "ON" + "/" runs the sequential key press test but shows 1,2 or 3 segments at a time and does not give "error 9" if you press the keys in the wrong order. When the test ends it doesn't show the "12" on the display just returns you to the X register. - "ON" + "x" run a self test (I think) for one second and just results to the x register. - [ON] + [-] will clear the calculator and show "Pr Error". - [ON] + [+] will run a continues self test (I think) ending when you press and hold any key. Now for the new stuff that I found from playing around: - [ON] + [g] shows the curious display below but I haven't found anything that you can do with this yet:

- [ON] + [g] + [ENTER} starts a testing menu:

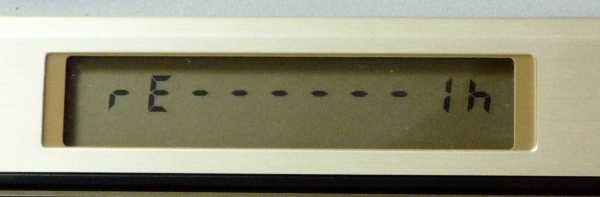

1.L - LCD test -- this turns on all the segments. If you then press [Rv] it will turn off half of them, press [Rv] again and you'll toggle the segments on to off and vice versa 2.C - Copyright. First you'll see this:

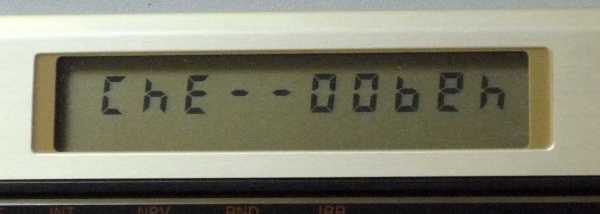

the next key press will give you this:

then next you'll see this:

3.H - Extended LCD and key test. All segments will turn on at first. hit any key and it will turn off 1 to 3 segments that sort of map to the position of the keys -- rows and columns. There are probably other easter eggs in here too, but I have yet to find them. So, how do you find one of these in the store? You can see the bottom edge of the calculator through the packaging, here's what it looks like:

Here's a picture of the back, see how big that batter cover is?

And here's what it looks like under the door, I need to get one of those special SDK cables from HP so I can start playing around with some alternative firmware.

(I'm tempted to pull off the feet and peek at the circuit board, but I'm going to wait for a bit longer.) I think they did a great job on this. Proven technology and ergonomics updated with modern speed and firmware replacement/updatability. I can't wait for the modern 15C (and, dare I suggest, 16C). Way to go HP! Kudos to Eric, Cyrille, Sam, Gene and whoever else had a hand in this.

Edited: 28 Apr 2009, 1:47 a.m. after one or more responses were posted |